基于MCU與FPGA模式的RFID讀寫器設計與通信系統開發

隨著物聯網技術的快速發展,RFID(射頻識別)系統在倉儲管理、智能交通及身份識別等領域的應用日益廣泛。基于MCU(微控制器單元)與FPGA(現場可編程門陣列)模式的RFID讀寫器設計,結合了MCU的靈活控制能力與FPGA的高效并行處理特性,能夠顯著提升讀寫器的性能和可靠性。本文將詳細介紹該讀寫器的硬件架構設計、通信系統開發流程及其關鍵技術。

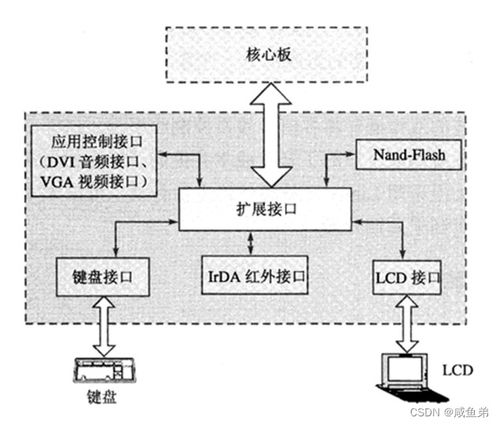

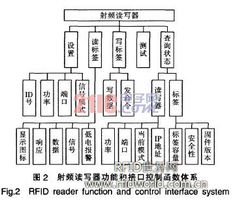

在硬件設計方面,系統采用MCU作為主控制器,負責協議解析、數據管理和用戶接口處理;FPGA則用于實現射頻信號的調制解調、編碼解碼以及時序控制等底層操作。這種分工模式充分利用了MCU的通用性和FPGA的高速并行能力,提高了系統的實時響應速度和數據處理效率。例如,在UHF RFID應用中,FPGA可快速處理反向散射信號,而MCU則執行EPC Gen2協議棧,確保與標簽的穩定通信。

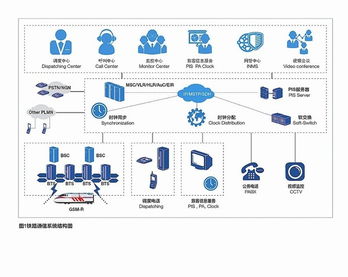

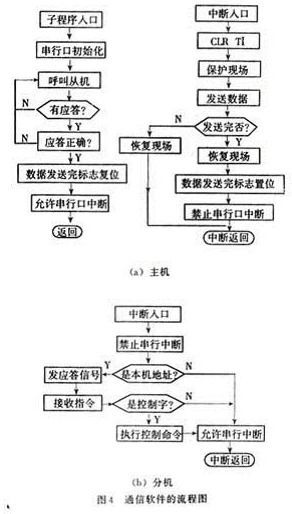

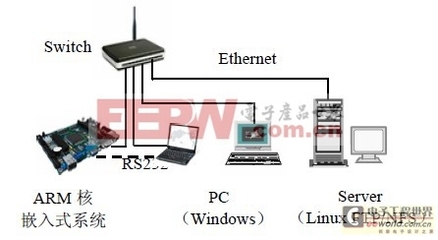

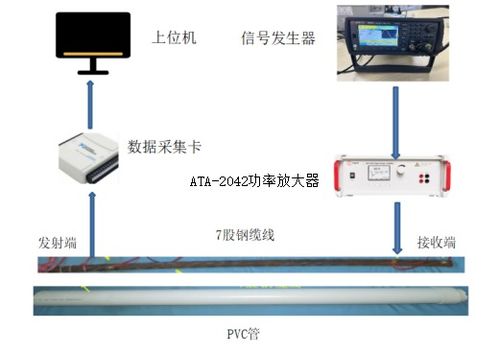

通信系統開發是設計的核心環節。需定義讀寫器與標簽之間的空中接口協議,如ISO 18000-6C標準,并利用FPGA實現載波生成、ASK/PSK調制及CRC校驗等功能。通過MCU集成UART、SPI或以太網接口,實現讀寫器與上位機或網絡的數據交互。開發過程中,重點優化抗干擾算法和多標簽防碰撞機制,例如采用Aloha或樹形算法,以提升在多標簽環境下的讀取率。

系統集成與測試至關重要。通過聯合仿真工具(如MATLAB與Vivado)驗證FPGA邏輯,并結合MCU的嵌入式軟件進行系統調試。實際測試表明,該設計支持多頻段操作,通信距離可達10米以上,誤碼率低于10^-6,適用于高密度標簽場景。

基于MCU與FPGA的RFID讀寫器設計不僅提高了系統的靈活性和性能,還為復雜環境下的物聯網應用提供了可靠解決方案。未來,可進一步集成人工智能算法,實現自適應功率控制和智能數據分析,推動RFID技術向更智能化方向發展。

如若轉載,請注明出處:http://m.sbqjou.cn/product/34.html

更新時間:2026-01-07 09:59:44